위의 표는 레지스터 전송문을 이용하여 7개의 메모리 참조 명령어를 자세하게 기술해 놓은 것 입니다. 각 명령은 명령어 코드 디코더의 출력 D에 의해 구별되고, 피연산자에 대한 유효 주소는 T2(I=0일 때)나 T3(I=1일 때) 시간에 AR레지스터로 전송됩니다. 그리고 명령의 수행은 타이밍 신호 T4에서 시작되고요 이 경우에 메모리에 저장되어 있는 데이타는 직접 처리될 수 없기 때문에 여러 개의 마이크로 연산을 통해서 명령어가 수행이 됩니다. 암튼 각 명령어를 수행하는 데 필요한 제어 함수와 마이크로 연산에 대한 동작, 그리고 마지막에 흐름도를 이용하여 전체 명령어를 살표 보겠습니다.

AND 명령어

이 명령어는 AC와 유효 주소로 지정된 메모리 워드의 각 비트쌍에 대하여 AND 논리 연산을 수행하고, 결과를 AC에 전송합니다. 이 명령어를 수행하기 위해 필요한 마이크로 연산은

D0T4 : DR←M[AR]

D0T5 : AC←AC^DR, SC←0

AND명령어에 대한 제어 함수는 명령어 디코더의 출력 D0를 사용하는데, 시간 T4에서는 메모리의 피연산자를 DR레지스터에 전송하고 T5에서는 AC와 DR사이의 AND연산 결과를 AC에 저장하고, 동시에 SC를 클리어하여 새로운 명령어 사이클이 시작되도록 합니다.

ADD명령어

이 명령어는 유효 주소로 지정된 메모리 워드의 내용을 AC에 더한 다음, 그 합은 AC에 저장하고 출력 캐리(Cout)는 e플립플롭에 전송합니다. ADD명령어를 수행하기 위해 필요한 마이크로 연산은

D1T4 : DR←M[AR]

D1T5 : AC←AC+DR, E←Cout, SC←0

여기서는 명령어 디코더의 출력 D1과 함께 T4와 T5타이밍 신호를 사용합니다. 위와 같이 어떤 명령어가 메모리에서 FFETCH되고 디코딩된 다음에는 오직 하나의 디코드 추력만 활성화 되고 이것이 해당 명령어를 수행하는 데 필요한 마이크로 연산 순서를 결정합니다.

LDA명령어

이 명령어는 유효 주소로 지정된 메모리 워드의 내용을 AC에 전송하고 베스에서 AC로의 직접 연결 경로가 없으므로 메모리 내용을 우선 DR로 읽어옵니다. 이후 가산/논리 회로를 거쳐 AC로 전송이 됩니다.

D2T4 : DR←M[AR]

D2T5 : AC←DR, SC←0

STA명령어

이 명령어는 AC내용을 유효 주소로 지정된 메모리 워드로 전송하고 AC출력은 버스를 통해 메모리 입력과 연결되어 있습니다.

D3T4 : M[AR]←AC, SC←0

BUN명령어

이 명령어는 프로그램의 수행을 유효 주소로 지정된 명령어로 옮기는 일을 합니다. 즉 순차적으로 증가하는 PC의 값을 다음 실행될 명령어의 주소로 무조건 JUMP를 시키는 거죠 AR의 유효 주소를 PC에 전송하고 SC를 0으로 클리어 하여 새로 지정된 다음 명령어를 FETCH 시킵니다.

D4T4 : PC←AR, SC←0

BSA명령어

이 명령어는 Subroutine라고 하는 프로그램의 일부분으로 분기하는데 유용하게 사용이 됩니다. 현 PC에 저장된 다음 명령어의 주소가 유효 주소로 지정된 메모리에 저장을 합니다. 뭐 일반적으로는 스텍이나 프로세스 레지스터에 저장이 되지요 암튼 유효 주소보다 1 큰 값이 PC로 전송되어 서브루틴의 첫 명령어를 가리킵니다.

D5T4 : M[AR]←PC, AR←AR+1

D5T5 : PC←AR, SC←0

밑의 그림은 BSA명령어의 실행 예 입니다.

ISZ명령어

이 명령어는 유효 주소로 지정된 워드 값을 하나 증가 시켜서 증가된 값이 0이면 PC도 하나 증가시켜 다음 명령어를 수행하고 메모리 워드를 직접 증가 할 수 없으므로 값을 DR로 읽어 온 후 증가 시킨 다음 다시 메모리에 저장을 합니다. 지금 우리가 알아보고 있는 명령어중에 가장 깁니다. (7개의 타이밍신호 : T0~T6 3비트 순차 카운터)

D6T4 : DR←M[AR]

D6T5 : DR←DR+1

D6T6 : M[AR]←DR, IF (DR=0) THEN (PC←PC+1), SC←0

제어 흐름도

밑의 그림은 흐름도로 7가지 메모리 참조 명령어를 수행하는 데 필요한 모든 마이크로 연산을 보여주고 있습니다. 각 네모상자 위에 제어 함수가 표시되어 있고 T4, T5, T6에서 수행되는 마이크로 연산들은 각 명령어의 연산 코드에 따라 6가지 다른 경로를 형성합니다. 각 경로의 마지막 타이밍 신호에서는 순차 카운터가 0으로 클리어되어 다음 명령어 사이클을 위한 타이밍 신호 T0로 제어가 이동이 됩닏. 그리고 가장 긴 명령어(ISZ)를 수행하는 데에도 7개의 타이밍 신호로 충분하므로, 이 컴퓨터는 3비트 순차 카운터로 설계될 수 있습니다.

그럼 다음 블로그에는 입출려과 인터럽트에 대해서 알아보겠습니다.

하루에 2개 올린다는게 정말 쉬운게 아니군요 ㅠ_ㅠ 하지만 열심히 해야한다는 각오로(이번주에도 시험이 2과목...) 블로그를 올리고 있습니다. ㅋㅋ 컴구조를 지금까지 공부하면서 참 간단하다는 생각을 많이 합니다. 복잡한 구조로 움직이는거 같지 않고요 규칙을 따라 동작하는거 같은데 왜이리 수업시간에는 이해하기도 머리에도 들어오지 않던지...뭐 뒤쪽으로 가면 갈수록 더 어려워지나깐요 정신을 차려야겠지요 지난번 블로그에서 아주 간단히 예를 들으면서 한 클럭싸이클 동안에 어떻게 정해저 있는 간단히 봤는데요 이제 부터 본격적으로 한번 보겠습니다.

컴퓨터에서 각 명령어 사이클은 다음과 같은 단계들로 이루어제 있습니다.

1. 명령어를 메모리에서 가져온다(fetch라고 합니다.)

2. 명령어를 디코딩한다.

3. 간접 주소 방식의 명령어일 경우에 메모리로부터 유효 주소를 읽어온다.

4. 명령어를 실행한다.

네번째 단계가 끝나면 다시 첫번째 단계로 돌아가 다음 명령어에 대한 fetch, 디코드, 실행 단계를 반복합니다. 이러한 반복은 HALT명령을 만날 때까지 계속하여 반복합니다. 그럼 각 단계에 대해서 알아보도록 하겠습니다.

Fetch와 디코드

초기에 프로그램 카운터는 프로그램의 첫 명령어에 대한 주소를 가지고 있으며, 순차 카운터는 0으로 타이밍 변수 T0를 가리킵니다. 다음에 매 클럭마다 타이밍 변수는 T0, T1, T2와 같은 순서로 변합니다. 이 타이밍 변수들에 맞추어서 Fetch와 디코드 단계에 대한 마이크로 연산은 다음과 같은 레지스터 전송문으로 표시 됩니다.

여기서 AR레지스터만이 메모리의 주소 입력에 연결되어 있으므로, T0시간 동안 PC에서 AR로의 데이타 전송이 필요합니다. 메모리에서 읽어온 명령어는 T1에 해당하는 클럭 변이에서 명령어 레지스터(IR)에 저장됩니다. 동시에 다음 명령어의 주소를 위해 PC가 하나 증가됩니다. 시간 T2에서는 IR의 연산 코드부분이 디토드되고, 간접 비트가 플립플롭 I에 전해지며 주소 부분은 AR로 전송이 됩니다.

위의 그림은 처음 두 레지스터 전송문을 버스 시스템으로 구현한 것입니다. PC에서 RA로의 데이타 경로를 제공하기 위하여 타이밍 신호 T0를 적용시켜 다음과 같은 연결을 형성해야 합니다.

1. 버스 선택 입력(S2S1S0)DMF 010으로 하여 PC내용이 버스에 놓이도록 한다.

2. AR의 LD입력을 인에이블 시켜서 버스의 내용을 AR로 전송한다.

이와 같은 연결이 이루어졌으면 다음 클럭의 변이에서 PC와 AR 사이에 데이터 전송이 일어납니다. 두번째 문장을 구현하기 위해서는 타이밍 신호 T1을 이용하여 다음과 같은 연결을 형성해야 합니다.

1. 메모리의 읽기 입력을 인에이블시킨다.

2. S2S1S0=111로 하여 메모리의 내용이 버스에 놓이도록 한다.

3. IR의 LD입력을 인에이블시켜 버스의 내용에 IR로 전송한다.

4. PC의 INR입력을 인에이블시켜 PC의 값을 하나 증가시킨다.

명령어 종류의 결정

시간 T3동안에 제어 장치는 명령어의 종류를 결정합니다.

위의 그림에서 보듯이 레지스터 참조 혹은 입출력 명령은 T3에서 수행이 되어 지고 메모리 참조 명령은 T4에서 수행이 되어집니다. 기호로 표시하면 다음과 같습니다.

D7'IT3 : AR<-M[AR]

D7'IT3 : 아무런 일도 하지 않는다.

D7I'T3 : 레지스터 참조 명령어를 수행

D7IT3 : 입출력 명열어를 수행

레지스터 참조 명령어

레지스터 참조 명령어는 D7=1 이고 I=0 인 명령어로 IR(0-11)에 있는 나머지 12비트로 12가지 명령어를 나타냅니다. 모든 제어 함수는 D7I'T3의 부울식이 필요한데 이것을 간단히 기호 r로 나타내며, IR(0-11)레지스터의 각 비트를 Bi로 표시하여 각 명령어에 대한 제어 함수를 구별합니다. 예를 들어 16진 코드로 7800인 명령어 CLA는 이진 코드로 0111 1000 0000 0000 을 가리키기 때문에 I', D7, B11들이 1의 값을 가집니다. 따라서 이 명령어에 대한 마이크로 연산을 구동시키는 시간 제어 함수는 D7I'T3B11=rB11이 됩니다. 이와 같이 레지스터 참조 명령어는 사간 T3에 수행이 완료되고, 순차 카운터의 타이밍 신호는 다시 T0으로 돌아갑니다.

처음 7개의 명령어는 AC나 E레지스터에 대한 마이크로 연산을 나타내며 다음의 네 명령어는 주어진 조건이 만족될 때 다음 명령어를 수행하기 위해 PC를 다시 한번 증가시키는 연산을 나타냅니다. 마지막으로 HLT명령은 시작-끝 플립플롭 S를 클리어하고 순차 카운터의 동작을 멈추게 합니다.

다음 블로그에서는 메모리 참조 명령어에 대해서 알아보도록 할게요 그럼 시험기간 모드들 시험 잘보세요^^

지난 블로그에서는 컴퓨터 명령어에 대해서 알아보았습니다. 그 내용이 무척 중요하죠 일단 명령어와 명령어의 내용을 정확히 알지 못한다면 시험은 손도 못댄다고 봐야죠 주로 많이 사용하는 명령어들이 메모리 명령어들은 다 중요하고요 레지스터리 명령어는 CLA, CLE, CMA, CME 생각해보니깐 다 중요하네요...아무튼 그럼 본격적으로 타이밍과 제어부분에 대해서 설명해 보겠습니다.

기본 컴퓨터의 모든 플립플롭과 레지스터는 주 클럭 발생기에 의하여 제어됩니다. 그러나 클럭 펄스만으로는 레지스터의 상태를 변경시킬 수 없고, 제어 장치에서 생성된 제어 신호가 인에이블시켜 주어야 합니다. 제어 장치는 하드와이어(hardwired)제어 방시과 마이크로 프로그램(microprogrammed)제어 방식의 두 종류가 있습니다. 하드웨어 방식은 게이트, 플립플롭, 디코더 등의 디지탈 회로를 이용하여 제어 논리를 구현하기 때문에 속도면에서 유리하지만 컴퓨터의 구조가 변경되었을 때 여러 부품들 사이의 배선까지 바꾸어 주어야 하는 단점이 있습니다 반면에 마이크로 연산을 순차적으로 수행시키기 때문에 설계가 변경되더라도 제어 메모리의 마이크로 프로그램만 갱신해주면 됩니다.

순차 카운터는 동기적으로 클리어되는 기능을 가지고 있고 예를 들어 타이밍 신호가 T0, T1,T2,T3,T4와 같은 순차로 카운트된다고 가정하면 시간 T4에서 디코더가 출력 D3가 활성화되었을 때 SC가 0으로 클리어되도록 하는 문장을 D3T4 : SC<-0 라고 씁니다 아! 여기서 SC는 동기적으로 클리어 되는 기능을 가짐니다. 그럼 계속해서 D3T4 : SC<-0 에 대한 제어 신호의 시간 관계를 보여주는 타이밍도를 보겠습니다.

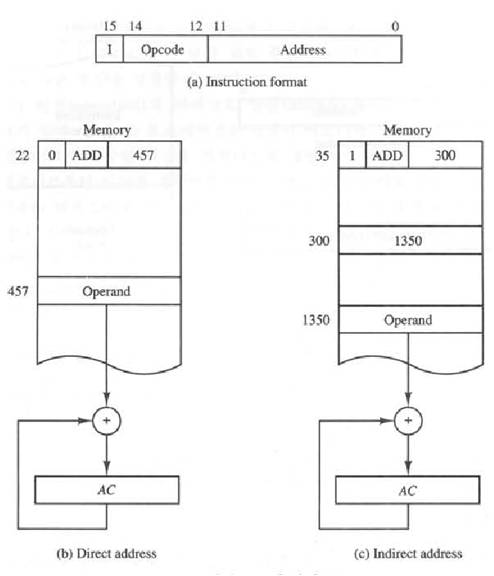

(a) 메모리 참조 명령은 12비트를 주소지정에 사용하고, 주소 모드 I를 위해 맨 왼쪽의 한 비트를 사용합니다.

(b) 레지스터 참조 명령어는 연산 코드가 111이고 최상위 비트는 0으로 되어 있으며, 주로 AC레지스터에 대한 연산을 지정합니다.

(c) 입출력 명령어는 연산 코드에 111, 최상위 비트에는 1을 가집니다. 레지스터 참조 명령어와 마찬가지로 메모리에 대한 참조가 필요없고, 나머지 12비트를 입출력 연산의 종류를 나타내는 데 사용합니다.

기본 컴퓨터에서는 총 25개의 명령어를 선택하였고 16진수 코드로 표시합니다. 16비트면 4개의 16진수 숫자로 표현이 가능합니다.

컴퓨터는 사용자가 생각할 수 있는 모든 데이타 처리 작업을 수행할 수 있도록 충분한 명령어들을 갖고 있어야 하는데 이에 필요한 명령어의 종류들을 생각해 보면

1. 산술, 논리, 시프트 명령어

가감산 : ADD, CMA, INC

곱셈, 나눗셈 : CIR, CIL

논리 연산 : AND, CMA, CLA

2. 메모리와 프로세서 레지스터 사이에 정보를 이동시킬 수 있는 명령어

메모리와 AC간 정보 이동 : LDA, STA

3. 상태 조건을 검사하는 명령과 프로그램 제어 명령어

분기 명령어 : BUN, BSA, ISZ

skip 명령어 : SPA, SNA, SZA, SZE

4. 입력과 출력 명령어

INP, OUT

위의 그림에서 왼쪽 그림의 최상위 16진수가 7인것이 레지스터 참조 명령어 F인것이 입출력 명령어이고 오른쪽 그림이 메모리 참조 참조 명령어인데 직접이냐 간접이냐에 따라서 코드가 나뉘어 집니다.

시험볼때 이걸 다 외워서 해야한다는......(숫자외우는게 약해서...) 암튼 다음 블로그에는 타이밍과 제어 부분을 설명하겠습니다.

아무튼 이번에는 5번째 이야기 기본 컴퓨터의 구조와 설계중 2번째 이야기 컴퓨터 레지스터에 대해서 이야기 하고자 합니다.

컴퓨터 명령어는 보통 연속적인 메모리상에 위치하고 이것들이 한 번에 하나씩 순차적으로 수행이 됩니다. 따라서 다음 수행될 명령의 주소를 알아낼 수 있는 카운터같은 장치가 필요하겠죠 또한 제어 장치내에는 메모리에서 읽어온 명령어 코드를 저장할 수 있는 레지스터와 데이터를 조작하기 위한 프로세서 레지스터, 그리고 메모리의 주소를 갖고 있는 레지스터가 필요할 것입니다.

위에 그림과 표에서 레지스터 구서오가 각 레지스터의 기능, 비트수를 확인할 수 있습니다.

메모리 장치는 4096워드로 구성되어 있으며, 각 워드는 16비트입닏. 즉 피연산자의 주소를 위해 12비트가 필요하고 3비트는 명령어 코드를 나타내며 나머지 1비트가 직접 주소, 간접 주소를 구별하는 데 사용됩니다. 데이타 레지스터(DR)는 메모리에서 읽어온 피연산자를 저장하며, 누산기(AC) 레지스터는 범용 처리 레지스터로서 사용이 됩니다. 메모리에서 읽어온 명령어는 명령어 레지스터(IR)에 저장되고 임시 레지스터(TR)는 계산 도중의 임시 데이타를 저장합니다. 메모리 주소 레지스터(AR)와 프로그램 카운터(PC)는 메모리의 주소를 나타내어야 하므로 12비트로 구성이 되어 있습니다. PC의 내용이 카운트 순서에 따라 증가함에 따라 명령어들은 분기 명령어를 만날 때까지 순차적으로 수행됩니다. 분기 명령가 수행될 때에는 주소 부분이 PC로 전송되어 다음 수행될 명령어의 주소를 지정하게 됩니다. 이 밖에 입출력 장치로부터 8비트 문자 정보를 송수신하기 위하여 입력 레지스터(INPR)와 출력 레지스터(OUTR)가 사용됩니다.

그렇다면 레지스터들 사이나 레지스터와 메모리 사이에 정보 전송을 어떻게 하는지 궁금해 지기 시작해지지요 기본 컴퓨터에는 정보 전송을 하기 위한 경로를 버스 시스템으로 구성을 합니다.

토요일, 일요일 앓아 누워 있어서 일요일에 블로그를 올리지 못했네여...감기들 조심하세요..(이래서 미리미리 올렸어야 했나...하지만 월요일에 옥상서...) 아무튼 지난 시간에도 이야기 했듯이 궂이 디지털 부속품과 데이터의 표현, 레지스터 전송과 마이크로 연산 부분은 건너뗘야 할거 같습니다. 일단은 너무 전자 회로쪽에 치우쳐도 있고 이대로 가서는 시그가 완료될 때까지 못 맡칠거 같기도 하고요 그럼 기본 컴퓨터의 구조와 설계로 넘어가도록 하겠습니다.

기본 컴퓨터의 구조와 설계(첫번째 명령어 코드)

컴퓨터의 구조는

1. 내부 레지스터

2. 타이밍과 제어구조

3. 명령어 집합

으로 되어지고 앞으로 얘기할 컴퓨터는 우리가 알고있는 pc에 비해 규모가 작지만 설계 과정을 단순하게 보여줄 수 있는 이점이 있습니다. ㅋㅋ(16비트 컴퓨터 정도지요)

디지털 시스템의 내부 조직은 레지스터 안에 저장된 데이처를 가지고 수행되는 마이크로 연산(레지스터에 저장된 데이타를 가지고 실행되는 동작 : 시프트, 카운트, 클리어, 로드)의 시퀀스에 의해 정의 되어집니다. 그렇다면 컴퓨터는 일반적인 용도의 시스템으로 다양한 마이크로 연산을 실행할 수 있고 수행할 연산의 특수한 시퀀스를 명령할 수 도 있습니다. 그리고 시스템의 사용자는 원하는 연산과 피연산자, 처리되는 순서를 기술한 명령어의 집합인 프로그램에 의해서 처리 과정을 제어할 수 있습니다.

그렇다면 명령어의 집합인 프로그램에서의 명령어 정확히 말하면 컴퓨터 명령어란 무엇일까요? 바로 컴퓨터에 대한 일련의 마이크로 연산을 기술한 이진 코드라고 할 수 있습니다. 또한 데이터와 함께 메모리에 저장이 되어있고 제어신호에 의해 제어 레지스터에 옮겨지고 해석되어 제어 함수를 발생함으로서 실행이 됩니다. 이와 같이 명령어를 저장하여 실행하는 개념을 내장 프로그램 이라고 하며 범용 컴퓨터의 가장 중요한 특성이기도 합니다.

앞서 설명한 내용으로 인해서 명령어란 곧 명령어 코드라는 것을 알게 되었습니다. 명령어 코드는 계속 반복되는 이야기지만 컴퓨터에게 어떤 특별한 동작을 수행할 것을 알리는 비트들의 집합으로서 여러 개의 부분으로 나뉘어지는데, 그 중 가장 기본적인 부분은 연산코드 부분입니다.

연산코드는 가감승제나 시프트, 보수 등과 같은 동작을 저의한 비트들의 집합으로서 이 연산 코드 부분이 n 비트로 구성되면 최대한 2^n개의 서로 다른 연산을 실행할 수 있습니다. 또한 하나의 연산코드는 마이크로 연산의 집합으로 볼 수 있기 때문에 때때로 매크로 연산이라고 불리기도 합니다.(햇갈리기 시작...)

명령어코드 이야기를 계속 하자면 명령어코드의 연산부는 실행될 연산을 기술하고 있는데 이러한 연산은 메모리 또는 프로세서 레지스터 안에 저장된 데이차를 가지고 실행되므로 명령어코드는 연산 뿐만 아니라 피연산자가 저장된 레지스터나 메모리 워드, 또한 연산 결과가 저장될 장소를 기술해야 합니다. 이와 같이 여러 개의 부분으로 구성된 명령어 코드의 구성형식은 컴퓨터의 구조 설계자에 의해 결정이 되어 집니다.

저장 프로그램 구조에 대해서 살표볼까요

컴퓨터의 가장 간단한 구성은 단 한 개의 프로세서 레지스터를 가짐으로서 두 개의 부분으로 구성된 명령어 코드를 사용하는 것입니다. 이때 한 부분은 실행할 연산을 그리고 다른 한 부분은 피연산자가 저장된 메모리내의 주소를 기술하게 되는데 메모리로 부터 읽혀진 피연산자 부분은 레지스터에 저장된 데이터와 연산을 실행하게 됩니다. 위의 그림에서 보듯이 4096워드를 가진 기억 장치에 대해서 12비트 주소가(2^12=4096)필요합니다. 16비트 워드를 사용한다면 4비트가 남음으로 총 16가지의 서로 다른 연산을 하게 됩니다. 여기서 한 개의 프로세스 레지스러를 누산기(accumulator 또는 AC)라고 하며 명령어 코드 구성 형식은 4비트로 이루어진 opcode(실행할 연산)와 address(피연산자가 저장된 메모리 주소)로 이루어져 있어서 Address에 의해 지정된 메모리에 데이터와 AC에 저장된 데이터사에에 opcode가 지정한 연산을 수행하게 됩니다.

여기서 유효주소라는 개념이 등장하게 되는데 아주 중요하죠 유효주소란 계산형 명령어에서의 피연산자의 주소와 분기형 명령어에서 목적주소를 뜻합니다.

다음에는 5번째 이야기 part2 컴퓨터 레지스터에 대해서 이야기 하도록 하겠습니다.

요즘 들어 엄청나게 빨라지는 학교진도와(벌써 작은 컴퓨터를 만들고 있어요 ㅠ_ㅠ) 그에 맞지 않게 늦어지는 포스팅을 보면서 걍 디지털 논리 회로를 건너 뛰고 갈까 하는 생각도 드는데 어떤것이 좋을지는 아직 판단이 서지 않는군요...ㅋㅋ 솔직히 매일 블로깅을 올린다면 충분히 커버할 수 있는 양이지만 맘처럼 쉽지 않군요...일요일에 글을 올리는것도 자꾸 잊어버리고 말이죠...평일에 예약해서 올려두 되는데...하하..참 사람맘이...이번까지 글을 올리고 생각해서 다음에는 논리회로를 건너뛸지 말지에 대해서 결말을 지어서 블로깅 하겠습니다. 일단 그럼 지난번에 이어서 맵에 간소화에 대해서 글을 올리고자 합니다.

.민텀(Minterm)

진리표에서변수의각조합

진리표는8 개의민텀을 갖습니다.

n개의변수가있다면2n개의민텀이존재

진리표에서출력F가1 이되는민텀을선택. F(x,y,z)=Σ(1,4,5,7)=x'y'z+xy'z'+xy'z+xyz

.K-Map

각사각형의구역은각각의민텀표시

논리표현식의출력이1이될때해당민텀구역에1을넣습니다.

인접사각형은오직1 bit만차이나도록구성함

인접구역의1을2의승수(2, 4, 8, …)로가능한크게묶음

묶여진그룹의bit가변화하지않는부분만을남김

각묶음의결과를OR 함

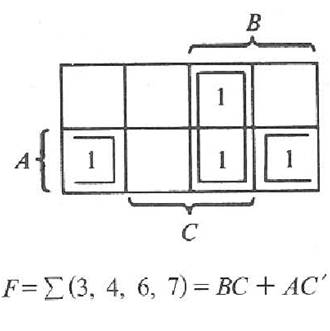

그럼 예를 들어서 보도록 하겠습니다.

F(A,B,C)=Σ (3,4,6,7) 의간략화

F(A,B,C)=Σ(3,4,6,7) = A’BC + AB’C’ + ABC’ + ABC

간략화된식F=BC+AC'

또한 입력이 4개 즉 변수가 4이고 민텀이 16개인 F(A,B,C,D)=Σ( 0,1,2,6,8,9,10)의간소화에 대한 예를 들어 설명하겠습니다.

먼저 맵에 출력이 1이 되는 0,1,2,6,8,9,10에 1을 넣습니다. 여기서 주의할것은 모양은 정사각형이지만 양 끝부분이 붙어 있는 하나의 원이라고 생각하셔야 한다는 점입니다.

그럼 최대한 크게 크게 묶으면 위의 그림 같이 묶을 수 있습니다. 그럼 같은 묶음은 AND 묶음들의 집합은 OR로 표현한다면

함수 F=B'D'+B'C'+A'CD가 되는것을 확인할 수 있습니다.

그럼 더 나아가 논리합의 논리곱에 대해 알아보겠습니다.

논리합의논리곱

.곱의합표현(sum of products)

.F = A + B + CD

.합의곱표현(product of sums)

.F = AB(C+D)

.F = (F’)’ 임을이용

.함수가0이되는민텀구역에0을삽입

.인접한0으로크게묶음

.결과로F’을얻음

.De Morgan의법칙에의해

.F = (F’)’을이용하여위의결과를보수화시킴

.Ex) F (A,B,C,D)=Σ(0,1,2,5,8,9,10)의간소화

.F = B’D’ + B’C’ + A’C’D (A맵을이용한간소화)

.F’=AB + CD + BD’

.(F’)’ = F =(A'+B')(C'+D')(B'+D)

출력이 1인 경우가 복잡한 경우에 이용하면 좋은것 같습니다. ㅋ

NAND, NOR gate를이용한구현

.NAND (Not AND), NOR (Not OR) gate

.전자회로구성이쉽고, 부울함수구현이용이하여AND, OR gate보다많이쓰임

.AND ÆNAND로OR Æinvert-OR 로바뀌면두회로는등가임

.OR ÆNOR로AND Æinvert-AND 로바꾸면두회로는등가임

Don’t Care Condition

.진리표에의해정의되지않는항이발생하는경우

.Ex) BCD code (10진수를나타내는4bit 2진코드)

.민텀이1이되거나0이되거나에관계없이같은함수의값을갖는경우

.맵에서는X를넣고1로혹은0으로간주하여묶습니다.

.예5)다음부울함수를간소화하라.

.함수: F(A,B,C)=Σ(0,2,6)

.Don’t care 조건d(A,B,C)=Σ(1,3,5)

.F=A'+BC'

. Cf) don’t care 를0으로보는경우:

F=A’C’ + BC’ ( 항의변수가하나추가됨: C'가 추가 되었죠)

이제 회로직전까지 갔는데 지금까지는 그렇게 이해하기 힘든부분은 없는거 같습니다.

아무쪼록 일교차 큰 날씨에 시그원 모두들 감기 조심하세요

1학년때 아마 수강하신 논리 Gate 내용이 슬슬 나오기 시작합니다. 1학년때 나름 열심히 공부해서 학점도 좋게 나와서 기억하고 있으려니 했는데...막상 연습문제를 푸니 xor부분을 자꾸 햇갈려 하더군요... 아무튼 시작하도록 하겠습니다.

논리Gate의종류

그럼 부울대수에 대해서 알아보도록 하겠습니다.

.부울대수

.2진변수와논리동작을취급하는대수

.변수. 일반적으로A,B,x,y,z 등의문자로표시

.3개의기본적인동작. AND, OR, NOT

.변수의값이주어질때부울함수는1 혹은0이됨

.이점: 디저털회로의해석과설계를쉽게할수있음

.변수사이의진리표관계를대수적으로표시

.논리도의입출력관계를대수형식으로표시

.같은기능을가진더간단한회로의발견

.Ex) f = x + y'z

14, 15, 16 번이 그 유명한 드 모르간의 정리 이죠 이중에서 조금 생소한건 14번이 되겠네요..(수학공식이랑 햇갈리기 시작하면..ㄷㄷㄷ) 그렇다면 드 모르간의 정리에 대해 더 알아보도록 하죠

. 수식의보수를 얻는데 유용

. (A+B)' = A'B'

. (AB)' = A' + B'

. NOR, NAND gate 표현에 사용됨(이점이 많이 중요하죠 중간고사를 보고..ㅠ_ㅠ)

그럼 부울 함수를 이용해서 회로를 간소화 해보도록 하겠습니다.

.그림1-6(a):

.F= ABC+ABC’ + A’C

.F= AB(C+C’) + A’C

.6개의gate 사용

.F= AB + A’C

.그림1-6(b)

.4개의gate 사용

복잡한 회로도가 간단히 표현되는 것을 확인할 수 있습니다.

다음 블로그에는 민텀, k-map에 대해서 올리겠습니다. 디지털 논리 회로 부분이 끝나면 연습문제 풀어서 올리겠습니다. ㅋㅋ

1. LSB(least significant bit)

MIPS 워드에서 가장 오른쪽 비트 0 를 의미

2. MSB(most significant bit)

MIPS 워드에서 가장 왼쪽 비트 비트 31을 의미

*. 음수를 표현하는 방법에는 여러가지가 있는데 부호와 크기 표현법, 1의 보수 표현법, 2의 보수 표현법 등이 있다.

부호와 크기 표현법 : 부호비트를 사용하여 음수를 표현하는 방법인데, 부호비트를 위치나 양의 0, 음의 0로 구분 등의 단점 때문에 현재는 잘 사용되지 않는다.

2의 보수 표현법 : 앞선 0들은 양수를 의미하고 앞선 1들은 음수를 의미하는 표현법이며, 음수는 해당 수의 보수 + 1로써 표현할 수 있다.

예) 1111 1111 1111 1111 1111 1111 1111 1100 two 의 10진수 값은 ?

1 이 앞서있으므로 음수로 판단되며, - 1 한 다음 보수를 구하면 된다. 즉, - 1 하면 마지막 4 비트가 1011 이되고

다시 보수를 구하면 0000 ~ 0000 0100 이되어서 4 가 되고 음수이므로 -4가 정답이다.

*. 부호확장(sign extension)

유부호 수와 무부호 수의 산술연산 및 적재시에 레지스터의 남는 곳을 채우기 위해 부호를 반복하여 복사하는 작업.

lb(load byte)는 바이트를 부호있는 수로 간주하고 남은 24비트를 부호확장하여 채운다.

lbu(load byte unsigned)는 부호없는 정수로 간주하여 24비트를 0으로 채운다.

reg $t0 에는 1111 1111 1111 1111 1111 1111 1111 1111 two

reg $t1 에는 0000 0000 0000 0000 0000 0000 0000 0001 two

1) slt $t0, $s0, $s1 #유부호 비교

2) sltu $t1, $s0, $s1 #무부호 비교

$s0 는 유부호 정수는 -1, 무부호 정수는 4,294,967,295 ten

$s1 은 모든 경우에 1 을 의미하므로

1) 의 결과는 -1ten < 1ten 이므로 1을 갖게되고

2) 의 결과는 4,294,967,295ten < 1ten 이 아니므로 0을 갖게된다.

4. 인터럽트(interrupt)

프로세서 외부에서 발생하는 예외(어떤 아키텍처에서는 모든 예외를 인터럽트로 표현한다)

internal-exception 에는 overflow, zero-divide 등이 있고 external-exception 에는 keyboard I/O에 의해 발생

5. 예외

인터럽트라고도 불린다. 프로그램 수행을 방해하는 계획되지 않은 사건. 오버플로우를 탐지하기 위해 사용한다.

MIPS의 경우는 EPC(exception program counter)라고 불리우는 레지스터를 제공하고 Intel과는 다르게 친절한 오류처리를 해주지 않고 OS가 직접 EPC를 통해서 찾아야만 한다.

10. 과학적 표기법(scientific notation)

소수점의 왼쪽에는 한 자릿수만을 갖도록 한 표기법

11. 정규화(normalization)

선행하는 0이 없는 표기법

12. 부동 소수점(floating point)

이진 소수점의 위치가 고정되어 있지 않은 수로 표현하는 컴퓨터 연산

13. 분수부분(fraction)

일반적으로 0과 1사이의 값으로 분수 필드에 위치한다 - 정밀도를 의미

14. 지수(exponent)

부동 소수점 숫자 표현의 지수 필드에 들어간 값 - 크기를 의미

*. MIPS의 일반정밀도

| [31] sign-1-bit | [30 ~ 23] exponent-8-bits | [22 ~ 0] fraction-23-bits |

15. 오버플로우(overflow)

양의 지수가 지수 부분에 표현될 수 없을 만큼 클때

16. 언더플로우(underflow)

음의 지수가 지수 부분에 표현될 수 없을 만큼 작을때

*. MIPS의 2배정밀도

| [31] sign-1-bit | [30 ~ 20] exponent-11-bits | [19 ~ 0] fraction-32-bits |

*. 부동 소수점의 덧셈 (단, 유효자리 4자리, 지수 2자리 저장가능)

: 9.999 ten * 10^1 + 1.610 ten * 10^-1

1. 작은 수의 유효자리를 지수가 큰 수의 것과 일치할 때까지 오른쪽으로 자리 이동

0.016 ten * 10^1 (단, 유효자리수가 4자리 이므로 1은 제거)

2. 유효자리를 서로 더한다.

10.015 ten * 10^1

3. 정규화를 위해서 정돈이 필요하다.

10.015 ten * 10^1 = 1.0015 ten * 10^2

4. 유효자리가 4자리 이므로 자리맞춤을 하는데 반올림을 적용한다

1.002 ten * 10^2

5. 단, 연속된 9에 의한 자릿수 변경의 경우 3번의 단계를 다시 거쳐야만 한다.

*. 부동 소수점의 곱셈 (유효자리수는 4자리, 지수는 2자리까지 저장 가능)

: 1.110 ten * 10^10 * 9.200 ten * 10^-5

1. 지수를 단순히 더하여 지수를 계산한다.

10 + (-5) = 5

2. 유효자리의 곱셈

10212000 ten 인데 우측 소숫점의 합은 6개 이므로

10.212000 ten 으로 계산되어진다. 즉, 10.212 * 10^5 이 된다.

3. 정규화를 하게되면

1.0212 ten * 10^6

4. 유효자릿수를 맞추면

1.021 ten * 10^6

5. 결과의 부호는 원래 피연산자의 부호에 따라 결정되므로 부호가 같으면 양수, 그렇지 않으면 음수이다.

최종 결과는 +1.021 ten * 10^6 이다.

*. 행 우선 순서(row major order)

배열의 배치방식을 의미하며 C 또는 많은 프로그래밍 언어에서 array(row, col)형태의 배열방식을 의미한다.

단, 포트란의 경우는 열 우선방식(column major order)을 사용한다.

19. 보호비트(guard bit)

부동 소수점 계산 도중에 필요한 오른쪽 두 개의 추가비트 중 첫번째 비트; 자리맞춤의 정확도를 높이기 위해 필요.

20. 자리맞춤비트(round bit)

부동 소수점 계산 도중에 생기는 겨로가가 부동 소수점 형식에 일치하도록 하는 방법; 목표는 형식에 맞는 가장 가까운 수를 찾는 것이다.

*. 예제 - 유효 자릿수가 3자리인 경우

보호자리와 자리맞춤 자리를 이용한 결과와 그렇지 않은 결과 비교

2.34 ten * 10^2 + 2.56 ten * 10^0

1) 2.3400 ten + 0.0256 ten = 2.3656 ten 이며 2.37 ten * 10^2 가되어 반올림 효과를 본다.

2) 2.34 ten + 0.02 ten = 2.36 ten 이되며 1)과 가장 오른쪽 자리의 수가 1이 작게된다.

21. ulp(unit in the last place)

실제 값과 표현할 수 있는 값의 최하위 유효자리 비트 중에 서로 다른 비트의 수.

부동 소수점의 정확도는 유효자리의 최하위 비트 중 몇 개가 잘못된 값을 갖는지에 따라 결정되며 이 척도가 ulp이다.

*. 자릿수 맞춤 - 4가지

1) +∞자리맞춤 : 항상 자리 올림 ( -1.6 := -1.0, -0.4 := 0, 0.4 := 1, 1.6 := 2 )

2) -∞자리맞춤 : 항상 자리 내림 ( -1.6 := -2.0, -0.4 := -1.0, 0.4 := 0, 1.6 := 1 )

3) truncate : 잘라내기 ( -1.6 := -1.0, -0.4 := 0, 0.4 := 0, 1.6 := 1 )

4) round-off ( -1.6 := -2.0, -0.4 := 0, 0.4 := 0, 1.6 := 2 )

*. 오류 및 함정

오류 : 부동 소수점의 덧셈은 결합법칙이 성립한다. (따라서, x + ( y + z ) = ( x + y ) + z )

문제는 두 개의 매우 큰 수의 덧셈에 어떤 작은 수를 더할 때에 발생할 수 있으며 아래와 같이

1) x + ( y + z ) = -1.5 ten * 10^38 + ( 1.5 ten * 10^38 + 1.0 )

2) ( x + y ) + z = ( -1.5 ten * 10^38 + 1.5 ten * 10^38 ) + 1.0

1) 번의 경우는 ( 1.5 ten * 10^38 + 1.0 ) 결과가 0 이 되어서 0 이 되지만

2) 번의 경우는 1이 되어서 결합법칙이 성립하지 못하는 예가 된다.

오류 : 한 비트 왼쪽 자리이동 명령어가 2를 곱해준 거소가 같은 결과를 갖듯이 오른쪽 자리이동 명령어는 2로 나누어준 것과 같은 결과를 갖는다.

부호비트가 0으로 채워지는 결과를 낳게되어 전혀다른 값을 가질 수 있으며, 단, PowerPC는 특별한 덧셈 명령어(add with carry)와 빠른 자리이동 명령어(shift right algebraic)를 가지고 있어서 지원가능하다.

함정 : MIPS 명령어 addiu는 16비트의 수치값(immediate field)을 부호확장하여 사용한다.

MIPS는 수치값을 사용하는 뺄셈 명령어를 사용하지 않으므로 (뺄셈 대신에 음수를 더한다) 음수는 부호확장 되어야만 한다. 따라서 MIPS 아키텍처는 수치값 필드를 부호 확장하여 사용한다.

오류 : 이론 수학을 전공하는 사람만이 부동 소수점 연산의 정확성에 신경을 쓴다.

인텔 칩의 버그는 실제 필드에서 사용하는 어플리케이션의 이용자들에 의해 발견되기도 하였다.

*. 결론

컴퓨터의 연산은 제한된 표현의 정밀도 때문에 항상 주의를 기울여야하며, 제한된 정밀도보다 더 크거나 작은 수를 계산하는 것은 잘못된 연산 즉, 오버플로우, 언더플로우가 발생할 수 있으므로 유의해야만 한다.

그리고 부동 소수점의 연산은 실제 값을 근사값으로 표현해야만 하는 문제가 항상 존재하며, 실제 값에 가장 근접하다는 것을 보장하기 위해 주의가 필요하다.

- 시험기간이라서 용어가 중요하더군요 내용은 어느분이 잘 정리해서 올려놓은것을 발취했습니다. 외우느라 머리가 아프네요

중간고사 시험기간인데 모두들 시험 만점받으세요^^

안녕하세요 17-2기 심형남입니다. 요즘학교서 속칭 컴구조라고 하는 컴퓨터시스템구조를 수강하는데 정리겸 해서 포스팅하기로 했습니다. 강의 내용과 연습문제 풀이형식으로 포스팅할 예정입니다.

참고 서적 : Computer System Architecture -M.Morris Mano

1. 디지털 컴퓨터

■ 디지털 컴퓨터

- 여러가지 계산을 수행하는 디지털 시스템

- 0과 1의 두개의 숫자만을 이용하는 2진수 시스템

- 컴퓨터 내부의 정보가 제한된 수의 불연속적 값으로 표시

-Ex) 10진수 : 1-9까지 10개의 불연속적인 값 사용

■ 디지털 시스템

- 전자부품의 물리적 제약과 인간의 논리가 2진적이라는 이유때문에 오직 2개의 값만을 가지도록 제한한다.

■ 비트(Bit)

- 하나의 2진 숫자

- Bit group을 통해 하나의 정보를 표시함

- 다양한 코딩 기법에 의해 10진수, 영문자 등 표현가능

■ 2진수

- 2를 밑수로 하는 수의 체계

- 진법 변환의 예

- 2진수(1001011)

- 1×26+0×25+0×24+1×23+0×22+1×21+1×20 = 75

■ 컴퓨터의 구분

- 하드웨어:컴퓨터의 모든 전자부품과 주변장치를 구성하는 전자기적 부품

- 소프트웨어 : 컴퓨터의 여러가지 정보처리 작업을 수행하는 명령어와 데이타들로 구성

■ 시스템 입장에서의 구분

- 하드웨어

- 시스템 소프트웨어(Operating System)

•컴퓨터 시스템을 효율적으로 사용하기 위한 목적을 가진 프로그램 집합(Compiler)

•사용자가 요구하는 하드웨어(Hardware) 기능간의 차이점을 보상

2. 하드웨어

■ 중앙처리장치(Centeral Processor Unit;CPU)

- 데이타를 조작하는 산술 및 논리연산 부분

- 데이타를 저장하는 레지스터(Register)

- 명령어를 가져와 수행하는 제어회로

- 기억장치(Random Access Memory;RAM)

- 명령어와 데이타를 저장

- 입출력 장치

- 컴퓨터와 외부 세계와의 통신과 데이타 전송을 제어

- 키보드, 프린터, 터미날, 자기 디스크

3. 연구자의 관심에 따른 컴퓨터의 분류

■ 컴퓨터 조직 (Computer organization)

- 하드웨어 구성품들의 동작 방식과 이들의 연결방식에 관심을 두는 것으로 각 부품들이 제대로 동작하기 위한 조직적인 구조를 연구

■ 컴퓨터 설계(Computer Design)

- 컴퓨터 하드웨어 설계

- 제시된 컴퓨터의 사양에 따라 적절한 하드웨어를 선택하고 그들간의 연결방식을 결정하여 시스템 개발

- 컴퓨터의 구현

■ 컴퓨터구조(Computer Architecture)

- 사용자 입장에서 컴퓨터의 구조나 동작에 관심

- 정보의 형식이나 명령어 집합, 메모리 주소기법 등을 연구

- 컴퓨터의 구조적 설계

•프로세서나 메모리같은 기능적 모듈의 사양을 가지고 컴퓨터 시스템 설계

4. 논리 Gate

■ 2진 정보

- 물리적 양인 전압 신호를 통해 표현

- 5V = 1, 0.5V=0

■ 2진 정보의 처리

- Gate라는 논리 회로에서 처리

■ Gate

- 입력논리의 필요조건에 따라 1 또는 0의신호를 만드는 하드웨어 블럭

- 동작을 대수적 함수로 표시하기 위해 진리표 사용

■ 논리Gate의 종류