Altera 디바이스들에 디지털 논리회로를 구현하기 위한 소프트웨어로써 계층 구조적인설계를 위한 다양한 design entry 기법을 제공하며, 강력한 논리 합성, 타이밍을 고려한 컴파일, 분할, 기능 및 타이밍 시뮬레이션 , 링크된 멀티 디바이스 시뮬레이션(linked multi-device simulation), 타이밍 분석, 디바이스 프로그래밍등의 기능을 제공한다.

VerilogHDL 로 본격적인 로직 설계에 앞서 Quartus의 사용법을 익히기 위해 간단하게 실습해 보았다.

1. Quartus II 설치

2. 웹에서 License를 받아 업데이트

3. New Project Wizard

4. Proje.ct 생성

5. File -> New -> Block Diagram/Schematic File

6. Graphic Editor 시작

7. Insert Symbol

8. 원하는 Logic Symbol 추가

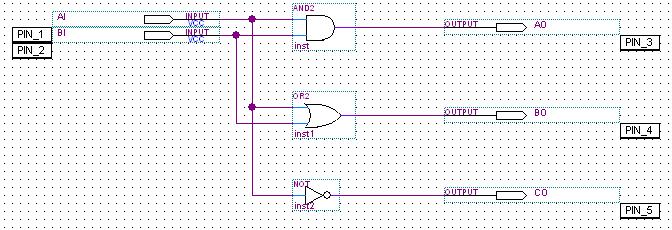

위에 보이는 그림처럼 입력 두개의 AND, OR, NOT gate를 테스트 해 보았다.

로직의 입출력 관계를 확인하기 위한 시뮬레이션을 하려면

1. New -> Other Files -> Vector Waveform File 을 생성한다.

2. Insert Node or Bus 를 선택하여 각각 입출력 핀에 노드를 매칭 시켜주고

3. Grid Size -> Time Period 설정(여기선 10ns)

4. End Time 설정(100us)

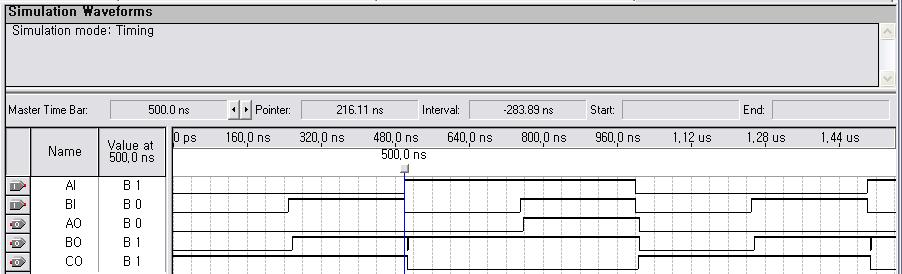

5. Waveform Editor Window에서 입력 A, B를 각각 주기 1us, 0.5us 50%duty로 설정

6. Start Simulation

시뮬레이션 결과 AND, OR, NOT gate의 입출력 특성을 확인할 수 있다.

하지만;; 출력B(OR gate output)에서 딜레이가 발생 출력이 튀는 현상이 발생한다.

이제 시작 단계라서 아직 문제가 뭔지는 모르지만 순간 딜레이를 주거나 타이밍을 맞춰야 하는 필요성을 느꼈다.(공부 더해야지;;)

이 간단한 로직을 VerilogHDL로 간단하게 짜서 해보려고 하는 중인데;;

module AND2(A,B,X);

input A,B;

output X;

and(X,A,B);

endmodule

간단한 AND gate 모듈인데;;컴파일 에러가 난다.

Error: Top-level design entity "test_v" is undefined

간단한 문제일꺼 같은데 2시간째 해매고 있다.;;

해결하는데로 업데이트 하겠슴당ㅠㅠ