"Verilog HDL의 기초와 디지털 논리회로설계"와 "디지털 논리회로와 집적회로설계" 같은 저자분께서 책을 쓰셨네요.

살펴보니 두 책이 비슷한데 QUARTUS를 이용하는 방법과 로직설계의 방법의 설명이 잘 되어 있습니다.

일단 Verilog HDL을 컴파일하고 시뮬레이션 하려면 QUARTUS 라는 프로그램이 필요한데 www.altera.com 에 가서 Quartus II Web Edition을 온라인으로 다운 받아서 사용하시면 됩니다.

다운로드 방법은 다음에 올리도록 하지요.( 얼마전까지 라이센스를 받아서 설치 한걸로 기억하는데 지금은 Quartus® II Web Edition Software v8.1를 다운 받을 수 있고 라이센스가 필요없다고 하네요ㅋ다운받고 있습니다. 받아서 설치해봐야 겠어요. )

암튼 책을 보고 있는데 문법은 살펴 보았고 데이터형을 공부해 보면서 정리 할 필요가 있더군요.

Verilog HDL 데이터형

1) 논리값 집합

Verilog HDL은 하드웨어 기능을 모델로 한 4개의 논리값과 8개의 신호 강도를 지원한다.

|

논리값 레벨 |

하드웨어 회로에서의 상태 |

|

0 |

논리적 0, 거짓 상태 |

|

1 |

논리적 1, 참 상태 |

|

x |

알 수 없는 논리값 |

|

z |

하이 임피던스, 플로팅 상태 |

논리적인 값과 더불어 신호 강도를 갖는 신호들의 충돌을 해결하는데 종종 쓰인다.

|

신호 강도 |

형 |

정도 |

|

supply |

흐름(driving) |

가장 강도가 높음 |

|

strong |

흐름(driving) |

↑ |

|

pull |

흐름(driving) |

↑ |

|

large |

저장(storage) |

↑ |

|

weak |

흐름(driving) |

↑ |

|

medium |

저장(storage) |

↑ |

|

small |

저장(storage) |

↑ |

|

highz |

하이임피던스 |

가장 강도가 낮음 |

만약 다른 강도의 두 신호가 동일한 wire에 흐르면 더 강한 강도의 신호가 우세하다. 같은 강도가 만나면 어떠한 신호가 나올지 모른다.(x 이다.) trireg 넷만이 large,medium, small의 강도를 저장할 수 있다.

2) 넷(Nets)

넷은 하드웨어 요소 사이에 연결을 나타낸다. wire와 net은 종종 서로 같은 뜻으로 사용된다. net의 기본값은 z이다. (trireg net은 기본값이 x이다.)

net은 키워드가 아니라 wire, wand, wor, tri, triand, trior, trireg 등의 집합을 나타낸다. 대부분 wire로 선언

wire Y;

wire A, B;

wire C=1'b0 // C는 논리값 0으로 선언

- 넷의 데이터형

wire : 논리적인 행동이나 기능 없이 단지 연결하는데 사용한다.(디폴트)

tri :wire 와 같으며 하이임피던스 상태가 더 있다.

supply1 : 넷을 전원에 연결한다.

supply0 : 넷을 그라운드에 연결한다.

tri1 : 넷을 풀업(pull up) 시킨다.

tri() : 넷을 풀다운(pull down) 시킨다.

wor : 여러 디바이스 출력을 선으로 연결(wired)하여 "or"기능을 하는 넷

trior : wired-or와 같으나, 하이임피던스 상태가 더 있다.

wand : 여러 디바이스 출력을 선으로 연결(wired)하여 "and"기능을 하는 넷

triand : wired-and와 같은나 하이임피던스 상태가 더 있다.

trireg : 하이 임피던스 상태가 있는 저장형인 넷(신호강도)

3) 레지스터

레지스터는 데이터를 저장할 수 있다. 하드웨어에서 레지스터와 다르다. 즉 Verilog에서 레지스터는 단지 값을 저장할 수 있는 변수를 의미한다. 하드웨어에서 레지스터는 클럭이 필요하지만 Verilog에서는 그렇지 않다.

레지스터 데이터형은 키워드 reg에 의해 정의 된다. 기본 논리값은 x 이다.

reg RESET;

initial // 초기화 선언

begin

RESET = 1'b1; // RESET를 1로 초기화

#100 RESET = 1'b0; // 100 단위 시간이 지난 뒤 RESET값을 바꾼다.

end

책을 보면서 정리를 하는데 내용이 많네요.스크롤의 압박?

논리값을 어떻게 나타내는지, net의 의미와 사용법, wire로 사용 한다는 것을 알았고 레지스터는 데이터를 저장하는 변수 역할을 하고 reg로 사용 한다는 것을 알게 되었습니다.

다음에는 못다한 내용을 이어 가도록 하지요~~

각각의 Programming Language 마다 정해진 문법이 있듯이 Verilog HDL도 정해진 규칙이 있습니다. C Language와 크게 다른 것은 없지만 어느면에서 틀리고 어떤 특징을 가지고 있는지 알아보겠습니다.

1. 기본적인 사항

- 여백(white space) : 빈칸(space), 탭(tap), carriage return, line feeds 등 사용

단어들을 분리하는데 사용

공백(blank), tap 은 문자열에서 의미 있게 취급된다.

- 이름 or 식별자(identifiers)등으로 사용되는 문자는 소문자와 대문자를 구별. 예약어는 반드시 소문자로 기술하여야 한다.

- 한 문장은 반드시 세미콜론(;)으로 끝난다. (end~ 로 시작되는 예약어는 제외)

2. 주석(comments)

- C Language와 비슷하게 사용

- 소스 코드의 설명을 위해 사용. 컴파일 과정에서 무시됨

- 단일 라인 주석문 : 2개의 슬래쉬 (//) 로 시작되어 해당 라인의 끝까지가 주석이 된다.

- 블록 주석문 : /* ~~~ */ 로 표시 여러줄에 걸쳐서 주석을 사용할 수 있다.

3. 수 표현 (number representation)

정수형(integer)

<비트폭>'(따옴표로 분리)<진수><값>

- 비트폭이 없는 경우 32비트 10진수를 나타낸다.

- 진수 표현 법

b, B : 2진수

o, O : 8진수

d, D : 10진수

h, H : 16진수

- 진수에 대응 되는 값

2진수 : 0, 1, x, z

8진수 : 0~7, x, z

10진수 : 0~9(x, z 사용 불가)

16진수 : 0~9, a~f(A~F), x, z

ex) 1'b1 -> 1비트폭을 가지는 2진수. 값은 1

8'o377 -> 8비트폭을 가지는 8진수. 값은 11111111

- 숫자에서 언더바(_)를 사용하여 읽기 쉽게 할 수 있고, 숫자 크기에 영향을 주지 않는다.

실수형(real)

<가수><E or e><지수>

- 가수 : 10진수

ex) 32e-4 -> 0.0032

4.1E3 -> 4100

4. 문자열(string)

- 겹따옴표(" ") 사이에 있는 문자들. 단일 라인에 존재해야 한다. 여러 라인에 걸친 문자열은 사용 불가

- 8비트 ASCII값으로 표현되는 unsigned 정수형 상수로 취급

- 문자열 변수는 reg형 변수이며, 문자열 내의 문자 수에 8을 곱한 크기의 비트 폭을 가진다.

ex)

reg [8*12:1] string_var;

initial begin

string_var = "Hello world!";

end

- 특수 문자 앞에 확장 문자를 사용하면 일부 특수 문자를 문자열에 포함시킬수 있음.

\n, \t, \\, \", %%

- 스트링은 시뮬레이션에만 사용된다.

5. 식별자(identifiers)

- 식별자는 사용자가 정의한 변수, 모듈 이름, 포트 이름, 함수 이름, 인스턴스 이름 등을 말한다.

- 대소문자를 구별하여 인식

- 가독성을 위해 언더바(_) 사용 가능

- 단순 식별자 : 문자, 숫자, 기호 $, 언더바 등으로 구성

첫번째 문자는 숫자나 기호 $ 사용 불가, 문자 또는 언더바만 사용

- 확장 식별자(escaped identifier) : back slash 로 시작 되며 여백(빈칸, 탭, 줄바꿈) 등으로 끝남

프린트 가능한 ASCII 문자들을 식별자에 포함시키는 수단을 제공

ex) \***error***

\{a,b}

6. 키워드(keyword)

- Verilog HDL 구성요소를 정의하기 위해 미리 정의된 식별자(예약어)

- 확장문자가 포함된 키워드는 키워드로 인식되지 않는다.

이상으로 간단하게 문법을 알아 보았습니다.

다음시간엔 실제로 QUATUS를 사용하여 Verilog HDL로 여러가지 로직설계하는 방법과 시뮬레이션 방법을 알아가 보도록 하겠습니다.

Verilog HDL, VHDL, SFL 등등. 그 중 Verilog HDL을 많이 사용하고 있다.

장점을 살펴보면 다음과 같다.

(1) C언어를 기초로 한 문법이며, 기술이 간단

(2) 문장과 연산자 등이 C언어와 거의 비슷하기 때문에, 배우기가 쉽다.

(3) 처음 시뮬레이션용 언어로 만들어졌기 때문에, 시뮬레이션 언어능력이 좋다.

(4) 언어체계가 단순하기 때문에 시뮬레이터가 고속이다.

Verilog HDL를 사용하여 간단한 논리회로를 설계해 보면

어떠한 기능을 가지는 하나의 로직을 모듈이라고 정의하고 "module"~"endmodule"안에 있어야 한다. 모든 문장은 세미콜론으로 끝내고, "end~"로 시작하는 예약어에는 세미콜론을 사용하지 않는다.

module 모듈이름 (포트목록);

포트선언;

레지스터 선언;

와이어 선언;

파라미터 선언;

회로기능 표현;

원시적인 연산자 또는

assign문(조합회로표현)

function문(조합회로표현)

always문(순차회로표현)

하위 모듈 호출 등.

endmodule (세미콜론 없음)

모듈이름은 영문자와 언더바("_")로 시작 할 수 있으며 대문자와 소문자를 구별하므로 주의한다.

위의 방법으로 간단한 모듈을 설계하는 2가지 예를 들어보면

1. 게이트 연산자를 이용한 경우

/* H_ADD */

module H_ADD (X, Y, C, S);

input X, Y;

output C,S;

and U1 (C, X, Y);

xor U2 (S, X, Y);

endmodule

2. 연속 할당 문을 이용한 경우

/* H_ADD */

module H_ADD (X, Y, C, S);

input X, Y;

output C,S;

assign C=X&Y;

assign S=X^Y;

endmodule

Altera 디바이스들에 디지털 논리회로를 구현하기 위한 소프트웨어로써 계층 구조적인설계를 위한 다양한 design entry 기법을 제공하며, 강력한 논리 합성, 타이밍을 고려한 컴파일, 분할, 기능 및 타이밍 시뮬레이션 , 링크된 멀티 디바이스 시뮬레이션(linked multi-device simulation), 타이밍 분석, 디바이스 프로그래밍등의 기능을 제공한다.

VerilogHDL 로 본격적인 로직 설계에 앞서 Quartus의 사용법을 익히기 위해 간단하게 실습해 보았다.

1. Quartus II 설치

2. 웹에서 License를 받아 업데이트

3. New Project Wizard

4. Proje.ct 생성

5. File -> New -> Block Diagram/Schematic File

6. Graphic Editor 시작

7. Insert Symbol

8. 원하는 Logic Symbol 추가

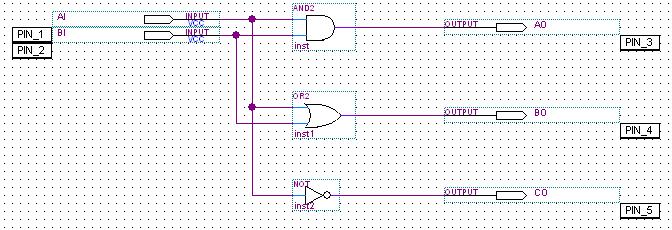

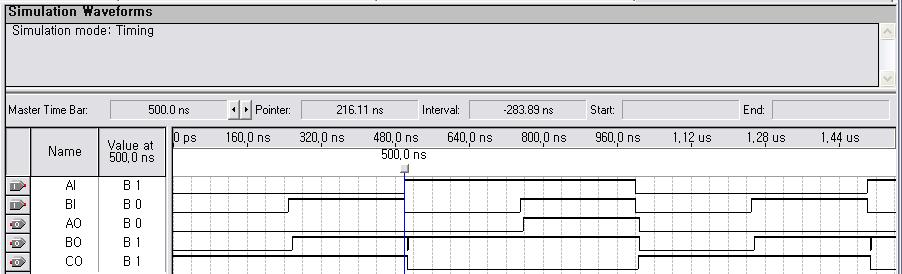

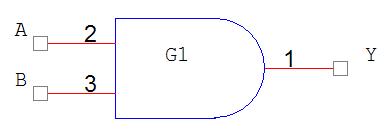

위에 보이는 그림처럼 입력 두개의 AND, OR, NOT gate를 테스트 해 보았다.

로직의 입출력 관계를 확인하기 위한 시뮬레이션을 하려면

1. New -> Other Files -> Vector Waveform File 을 생성한다.

2. Insert Node or Bus 를 선택하여 각각 입출력 핀에 노드를 매칭 시켜주고

3. Grid Size -> Time Period 설정(여기선 10ns)

4. End Time 설정(100us)

5. Waveform Editor Window에서 입력 A, B를 각각 주기 1us, 0.5us 50%duty로 설정

6. Start Simulation

시뮬레이션 결과 AND, OR, NOT gate의 입출력 특성을 확인할 수 있다.

하지만;; 출력B(OR gate output)에서 딜레이가 발생 출력이 튀는 현상이 발생한다.

이제 시작 단계라서 아직 문제가 뭔지는 모르지만 순간 딜레이를 주거나 타이밍을 맞춰야 하는 필요성을 느꼈다.(공부 더해야지;;)

이 간단한 로직을 VerilogHDL로 간단하게 짜서 해보려고 하는 중인데;;

module AND2(A,B,X);

input A,B;

output X;

and(X,A,B);

endmodule

간단한 AND gate 모듈인데;;컴파일 에러가 난다.

Error: Top-level design entity "test_v" is undefined

간단한 문제일꺼 같은데 2시간째 해매고 있다.;;

해결하는데로 업데이트 하겠슴당ㅠㅠ

이번에 FPGA 관련 시그를 하면서 공부한 내용을 차근차근 정리해 보도록 하겠습니다.

VerilogHDL로 FPGA 개발을 하기전에 배경지식을 알아본다. 반도체 칩을 설계 하는 방법에는 무엇이 있고 특징들은 무엇인지 지금부터 살펴 보겠다.

1. ASIC & FPGA

현대의 전자제품시장은 여러가지 기능의 다양한 제품이 출현하여 그 제품들 사이의 경쟁력을 가중시키고, 부가가치가 높은 다양한 기능의 고성능,고집적화된 제품들을 빠른 시간내에 개발하여 생산할 것을 요구하게 되고 이러한 문제들을 해결하기 위해 사용자의 주문에 따라 특정용도에 사용하는 ASIC (Application Specific Integrated Circuit)이 등장하게 되었다. 즉 반도체 부품의 저가격화, 다기능화, 제품수명 (Life Cycle)의 단축으로 ASIC기술이 도입되었고 이로 말미암아 반도체 부품의 개발기간이 단축되고 개발 비용이 절감되었다.

PLD (Programmable Logic Device)는 반도체 제조업체 측에서 보면 다량으로 제조되어 일반적인 용도로 판매되므로 범용성 칩의 범주에 속하고, 사용자 측에서 보면 사용자의 요구에 맞게 일시적으로나 영구적으로 칩내의 기본소자들을 물리적으로 연결시켜 사용하게 되므로 ASIC의 범주에 속하게 된다. PLD는 일반 ASIC보다 회귀시간(Turn-around Time)이 훨씬 줄어들고 개발비가 필요 없지만 PLD를 프로그래밍 할 또다른 장비를 필요로 한다. 이러한 PLD들은 기능적인 유연성(Flexibility)과 확장성 (Expansibility)의 한계를 가지고 있어, 이를 해결하기 위해 FPGA (Field Programmable Gate Array)가 등장하여 Mask Programming된 ASIC의 Gate Arreay와 경쟁상대로 널리 사용되고 있다.

2. LSI 분류

ASIC : Application Specific IC

USIC : User Programmable IC

ASSP : Application Specific Custom Standard Product

UPIC : User Programmable IC

CPLD : Complex Programmable Logic Device

FPGA : Field Programmable Gate Array

PLD : Programmable Logic Device

PROM : Programmable Read Only Memory

3. FPGA?

이미 설계된 하드웨어를 반도체로 생산하기 직전 최종적으로 하드웨어와 동작및 성능을 검증하기 위해 제작하는 중간 개발물 형태의 집적 회로(IC).

반도체 제조업자 측에서 보면 양산되어 일반적 용도로 사용 되므로 범용 IC의 범주에 속하고, 사용자 측에서 보면 사용자 요구에 맞게 프로그래밍하여 사용할 수 있으므로 주문형 반도체(ASIC) 범주에 속한다.

칩안에 수많은 논리 게이트(NAND, NOR, Flip-Flop...)등이 연결이 되지 않은 채로 들어가 있다. 자신이 만들고자 하는 회로를 설계하여 해당 FPGA의 CAD툴(Synthesizer:합성장치)을 돌리면 게이트들의 결선 정보로 변환되어 나온다. 이것을 FPGA에 써주면 원하는 칩으로써 동작한다. 이러한 과정은 한번이 아니고 반영구적으로 무한히 가능하므로 이런회로 저런회로 얼마든지 만들어 볼 수 있다. FPGA 자체 단가는 비싸다. 갓 출시된 수백만 게이트짜리 제품들은 수급상황에 따라 개당 천만원을 넘어가기도 한다.

4. ASIC?

일반 집적회로와 달리 전자정보통신 제품에 사용할 목적으로 설계된 비메모리 반도체 칩을 말한다. 논리회로형 반도체(FPGA)에 비해 값은 싸지만 상품화하는데 오랜 시간이 필요하다.

주로 PC에 사용되는 마이크로프로세서나(microprocessor)나 메모리칩(memory chip) 등 일반 집적회로와 달리 특정한 전자정보통신 제품에 사용할 목적으로 설계된 비메모리 반도체 칩이다. 전자제품을 제조하는 업체가 반도체 설계 업체에 개발을 주문하는 형태로 제작되는데, 전자제품의 성능을 좌우하는 핵심 기능을 포함한다.

설계자 의도를 반영해 회로를 설계하는 논리회로형 반도체(FPGA)에 비해 값은 싸지만 상품화 하는데 오랜시간이 필요하다. 수용자가 제품의 규격을 정해놓고 제조업체에 주문하는 특정 용도 주문제품(ASCP)과 제조업체가 스스로 규정한 용도를 위해 설계제작하는 표준제품(ASSP)으로 분류된다.

완성된 주문형 반도체를 도입하면 복잡한 중간 개발단계를 생략함으로서 개발에 필요한 인력과 비용을 대폭 줄일 수 있다. 제품의 고급화, 성능의 다양화 등도 가능해 계속 수요가 증가하는 상황이다.

주문형 반도체 업체에서는 연산장치, 제어장치, 출력장치, 입력장치 등의 부품으로 쓰이는 각종 집적회로를 개발한다. 또 새로운 제조기술과 제조방법 등에 관한 연구, 제조장비의 설치와 유지, 보수는 물론 반도체 칩의 실험 프로그램을 개발하고, 완성품의 작동여부에 대한 점검까지 담당하는 경우가 많다.

디자인된 회로를 Transistor Level로 그대로 Silicon Wafer안에 그려 넣는다.이렇게 만들어진 집적회로는 기능이 딱 결정이 되어 수정이 불가능하다. 반도체 라인에 한번의 ASIC을 돌리려면 라인 이용료로 한번의 많은 비용(수억)이 들어가지만 이후 양산 물량은 굉장히 저렴하게 대량생산이 가능하다.

ASIC으로 바로 칩을 만들기 전에 FPGA로 디자인한 회로를 먼저 검증하고, 잘 돌아가는 것이 확인되면 ASIC을 돌리게 된다. FPGA나 ASIC이나 둘다 집적회로이다. ASIC은 목적에 맞게 그 기능이 딱 제한된 IC이고 FPGA는 그 기능을 Programmable하게 바꿀수 있는 장치가 더 들어가 있는 IC라고 생각하면 된다.

참고 : 기초부터 응용까지 Verilog HDL (다다미디어)